1. Tujuan [Kembali]

· Mengetahui

rangkaian voltage divider bias

· Memahami

cara kerja rangkaian voltage divider bias

2. Komponen [Kembali]

· Transistor

NPN

Transistor

NPN mengalirkan arus negatif dari emitor menuju ke kolektor. Emitor berperan

sebagai input dan kolektor berperan sebagai output apabila transistor tersebut

diberikan arus positif pada basisnya.

· Resistor

Resistor

berfungsi sebagai penghambat arus listrik yang mengalir suatu rangkaian.

Cara menghitung nilai resistansi resistor dengan

gelang warna :

1. Masukan angka langsung dari kode warna gelang

pertama.

2. Masukan angka langsung dari kode warna gelang

kedua.

3. Masukan angka langsung dari kode warna gelang

ketiga.

4. Masukkan jumlah nol dari kode warna gelang keempat

atau pangkatkan angka tersebut dengan 10 (10^n) dan dikalikan ke ketiga warna

gelang tadi.

5. Gelang kelima ini merupakan nilai toleransi

dari resistor.

· Kapasitor

Fungsi

dari kapasitor adalah Sebagai Penyimpan arus atau tegangan listrik. Sebagai

Konduktor yang dapat melewatkan arus AC (Alternating Current) Sebagai Isolator

yang menghambat arus DC (Direct Current).

Satuan

Kapasitansi Kapasitor adalah Farad, tetapi Farad merupakan satuan yang besar

untuk sebuah Kapasitor yang umum dipakai oleh Peralatan Elektronik. Oleh Karena

itu, Satuan-satuan yang merupakan turunan dari Farad menjadi pilihan utama

produsen dalam memproduksi sebuah Kapasitor agar dapat digunakan oleh peralatan

Elektronika. Satuan-satuan tersebut diantaranya adalah : Micro Farad (µF), Nano

Farad (nF) dan Piko Farad (pF ).

Berikut

ini adalah ukuran turunan Farad yang umum digunakan dalam menentukan Nilai

Kapasitansi sebuah Kapasitor :

1

Farad = 1.000.000µF (mikro

Farad)

1µF

=

1.000nF (nano Farad)

1µF

=

1.000.000pF (piko Farad)

1nF = 1.000pF (piko Farad)

1nF = 1.000pF (piko Farad)

· VCC

Sebagai

sumber tegangan.

3. Dasar Teori [Kembali]

Rangkaian

voltage divider bias:

Voltage-divider Bias adalah arus bias

didapatkan dari tegangan di R2 dari hubungan VCC seri

dengan R1 dan R2 seperti gambar 4.28. Konfigurasi voltage divider

bias pada gambar 4.28 jika dianalisis secara tepat, sensitivitas terhadap

perubahan beta cukup kecil. Jika parameter rangkaian dipilih dengan benar,

level ICQ dan VCEQ yang dihasilkan dapat hampir

sepenuhnya tidak bergantung pada beta. Titik Q didefinisikan oleh tingkat tetap

ICQ dan VCEQ seperti yang ditunjukkan pada gambar 4.29.

Tingkat IBQ akan berubah dengan perubahan dalam beta, tetapi titik

operasi pada karakteristik yang didefinisikan oleh ICQ dan VCEQ

dapat tetap tetap jika parameter rangkaian yang tepat digunakan.

Untuk analisis dc jaringan gambar 4.28

dapat digambar ulang seperti yang ditunjukkan pada gambar 4.30. Sisi input dari

rangkaian kemudian dapat digambar ulang seperti yang ditunjukkan pada gambar

4.31 untuk analisis dc. Rangkaian sebelah kiri bisa dianalisis menggunakan

metoda Thevenin.

Sumber tegangan diganti dengan hubungan

arus pendek seperti yang ditunjukkan pada gambar 4.32. Sehingga bisa didapatkan

rumus Rth. Lalu, sumber tegangan Vcc dikembalikan seperti

rangkaian semula seperti pada gambar 4.33 dan bisa didapatkan rumus Eth.

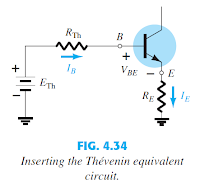

Setelah medapatkan Rth dan Eth,

maka rangkaian dapat diubah seperti pada gambar 4.34. Lalu bisa kita dapatkan Ib

dengan persamaan:

Setelah IB diketahui, sisa

jumlah jaringan dapat ditemukan dengan cara yang sama seperti yang dikembangkan

untuk konfigurasi bias emitor. Yaitu:

Kejenuhan

Transistor

Sirkuit kolektor-emitor keluaran untuk

konfigurasi pembagi tegangan memiliki penampilan yang sama dengan rangkaian

bias-emitor yang dianalisis pada Bagian 4.4. Persamaan yang dihasilkan untuk

arus jenuh (ketika VCE diatur ke nol volt pada skema) karena itu sama dengan

yang diperoleh untuk konfigurasi bias-emitor. Itu adalah,

Analisis

Load-Line

Kesamaan dengan rangkaian output dari

konfigurasi bias-emitter menghasilkan persimpangan yang sama untuk garis beban

konfigurasi pembagi tegangan.

4. Prinsip Kerja Rangkaian [Kembali]

Di

sini konfigurasi transistor emitor yang umum bias menggunakan jaringan pembagi

tegangan untuk meningkatkan stabilitas. Nama konfigurasi biasing ini berasal

dari fakta bahwa dua resistor RB1 dan RB2 membentuk jaringan pembagi tegangan

atau potensial di seluruh catu dengan sambungan titik pusatnya menghubungkan

terminal dasar transistor seperti yang ditunjukkan.

Voltage

divider bias ini adalah metode biasing transistor yang paling banyak digunakan.

Dioda emitor dari transistor maju bias dengan nilai tegangan yang dikembangkan

melintasi resistor RB2. Selain itu, rangkaian voltage divider membuat sirkuit

transistor tidak tergantung pada perubahan beta karena tegangan biasing yang

ditetapkan pada basis transistor, emitor, dan terminal kolektor tidak

tergantung pada nilai rangkaian eksternal.

Untuk

menghitung tegangan yang dikembangkan melintasi resistor RB2 dan oleh karena

itu tegangan yang diterapkan ke terminal dasar kita cukup menggunakan rumus

pembagi tegangan untuk resistor secara seri. Umumnya penurunan tegangan

melintasi resistor RB2 jauh lebih sedikit daripada resistor RB1. Jelas tegangan

basis transistor VB sehubungan dengan ground, akan sama dengan tegangan di RB2.

Jumlah arus biasing yang mengalir melalui resistor RB2 umumnya ditetapkan 10

kali dari nilai arus basis IB yang diperlukan sehingga cukup tinggi untuk tidak

berpengaruh pada arus pembagi tegangan atau perubahan Beta.

5. Gambar Rangkaian [Kembali]

Gambar 4.28

Gambar 4.31

Gambar 4.32

Gambar 4.33

Gambar 4.34

6. Video Simulasi [Kembali]

Video 4.28

Video 4.30

Video 4.31

Video 4.32

Video 4.33

Video 4.34

Tidak ada komentar:

Posting Komentar